## **AND8366**

## AMIS-4168x Fault Tolerant **Transceiver Design Considerations Using** CANLSFT

#### **ON Semiconductor®**

http://onsemi.com

#### **APPLICATION NOTE**

circuitry and digital functionality to co-exist on the same

This application note describes design considerations

using AMIS-41682 and AMIS-41683 in low speed fault

tolerant CAN networks conform to ISO 11898-3. More

• AMIS-41682 Datasheet (http://www.onsemi.com)

technical information can be found in:

ISO 11898–3 standard

#### Introduction

The new AMIS-41682 and AMIS-41683 are interfaces between the protocol controller and the physical wires of the bus lines in a control area network (CAN). The AMIS-41683 is identical to the AMIS-41682 but has a true 3.3 V digital interface to the CAN controller. The device provides differential transmit capability but will switch in error conditions to a single-wire transmitter and/or receiver. Initially it will be used for low speed applications, up to 125 kB, in passenger cars.

Both AMIS-41682 and AMIS-41683 are implemented in

#### Key Characteristics AMIS-41682 / AMIS-41683 **Device Parameters**

#### Table 1. KEY DEVICE PARAMETERS FOR THE AMIS-41682 AND AMIS-41683

AMIS-41682 AMIS-41683 Key Current consumption in normal mode (I<sub>CC</sub>) 7 mA (recessive) 7 mA (recessive) 17 mA (dominant) 17 mA (dominant) Current consumption in stand-by modes (I<sub>BAT</sub> + I<sub>CC</sub>) 30 µA 30 µA Minimum operating voltage 5 V 5 V Prevention of V<sub>BAT</sub> reverse current Yes Yes WAKE-B sensitivity Both edges Both edges True 3.3 V microcontroller interface No Yes NERR reporting of open failures During frame and inter frame space During frame and inter frame space

chip.

#### **System Parameters**

#### Table 2. KEY SYSTEM PARAMETERS FOR THE AMIS-41682 AND AMIS-41683

| Key                                                                      | AMIS-41682/3  |

|--------------------------------------------------------------------------|---------------|

| System Size                                                              | ≤ 32 nodes    |

| Speed                                                                    | 40 – 125 kbps |

| Emission                                                                 | ++            |

| Immunity                                                                 | ++            |

| TxD dominant monitoring                                                  | yes           |

| Extended bus failure management (including Failure 3a CANH to $V_{CC}$ ) | yes           |

| Resolved problem of arbitration across open failures                     | yes           |

I2T100 technology enabling both high-voltage analog

#### Pullup Resistors AMIS-41683

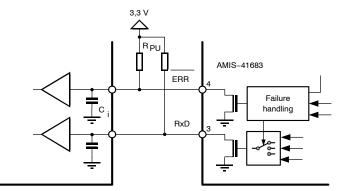

To interface with true 3.3 V microcontrollers AMIS-41683 has open drain outputs for RxD and ERR-B. To calculate the pullup resistor two considerations are important:

- A too high resistance value will create extra delay when charging the equivalent input capacitance Ci (see Figure 1).

- A too low resistance will negatively influence the V<sub>OL</sub> level.

Figure 1. Pullup Resistor to Interface with True 3.3 V Microcontrollers

#### Calculating R<sub>PU</sub> for Minimum Propagation Delay

The extra delay can be seen as the time needed to charge  $C_i$  up to 70% of the 3.3 V supply. This is given by:

$$t_{delay} = 1.2 * R_{PU} * C_i \qquad (eq. 1)$$

The typical propagation delay can be found in the data sheet and is given in Table 3.

#### Table 3. PROPAGATION DELAY

| Symbol             | Parameter                                      | AMIS-41683 |

|--------------------|------------------------------------------------|------------|

| t <sub>PD(H)</sub> | Typical propagation<br>delay TxD to RxD (high) | 750 ns     |

Assuming that this delay is symmetrical between TxD to BUS and BUS to RxD and that the extra delay should be less than 10% gives  $t_{delay} < 37$  ns. Calculating further with  $C_i = C_{input} + C_{interconnect} = 3.5 \text{ pF} + 3.0 \text{ pF} = 6.5 \text{ pF}$  in Equation 1 yields in:

$$R_{PU} = \frac{t_{delay}}{(1.2 * C_i)}$$

(eq. 2)

$$R_{PU} = \frac{37 \text{ ns}}{(1.2 * 6.5 \text{ pF})} = 4.74 \text{ k}\Omega \qquad (\text{Res.1})$$

#### Verifying R<sub>PU</sub> for Maximum V<sub>OL</sub>

The maximum sink current when RxD or ERR–B are pulled low via the open drain outputs of the AMIS–41683 is given by:

$$I_{SINK} = \frac{3.3 \text{ V}}{4.74 \text{ k}\Omega} = 696 \,\mu\text{A}$$

(Res.2)

This current is far below the maximum  $I_{sink} = 1.6$  mA to guarantee a  $V_{OL} < 0.4$  V as can be seen in the data sheet and in Table 4.

## Table 4. OUTPUT LOW LEVEL OF THE OPEN-DRAIN OUTPUTS RXD AND ERR-B

| Symbol              | Parameter                                                   | AMIS-41683 |

|---------------------|-------------------------------------------------------------|------------|

| V <sub>OL,max</sub> | Low level output<br>voltage @ l <sub>sink</sub> =<br>1.6 mA | < 0.4 V    |

#### Series Resistor at Pin BAT

The optional resistor  $R_{BAT}$  gives the AMIS-41682/3 <u>additional</u> protection against automotive transients (ISO 7637 part 5). It is not really needed because the high voltage part of the circuit is designed to withstand these high energetic pulses.

#### AND8366

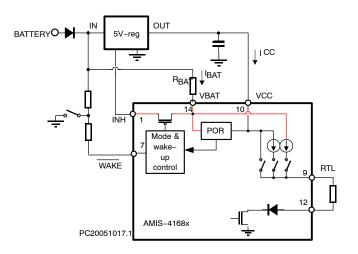

Figure 2. Connection via R<sub>BAT</sub> to V<sub>BAT</sub> Indication of Currents

The higher this series resistor the better the protection. However bigger series resistance results in a higher voltage drop thus increasing minimum operating battery voltage. To calculate this drop the maximum current consumption from  $V_{BAT}$  in normal and low power mode needs to be determined.

#### **Normal Mode**

In normal mode the maximum voltage drop over  $\mathbf{R}_{BAT}$  is given by:

$$V_{\text{DROPN}} = R_{\text{BAT}} * I_{\text{BAT}}$$

(eq. 3)

Calculating with  $\mathbf{R}_{BAT} = 1 \text{ k}\Omega$  the parameters from copied from the AMIS-41682/3 data sheets yields in:

$$V_{DROPN} = 1 \ k\Omega * 230 \ \mu A = 230 \ mV$$

(Res.3)

#### Low Power Mode

In low power mode the maximum voltage drop over  $\mathbf{R}_{BAT}$  is given by:

$$V_{DROPLP} = R_{BAT} * (I_{BAT} + I_{CC} + I_{RTL}) \quad (eq. 4)$$

Calculating with  $\mathbf{R}_{BAT} = 1 \text{ k}\Omega$  the parameters from copied from the AMIS-41682/3 data sheets yields in:

$$V_{\text{DROPN}} = 1 \text{ k}\Omega * (60 \ \mu\text{A} + 1.25 \ \text{mA}) = 1.31 \ \text{V}$$

(Res.4)

#### Conclusion

This shows that specifically in low power mode the voltage drop is relatively high due to the high output current on the RTL pin. For  $\mathbf{R}_{BAT} = 1 \text{ k}\Omega$  the minimum operating battery voltage is increased with 1.31 V. For  $\mathbf{R}_{BAT} = 2 \text{ k}\Omega$  this is almost an increase of 2.6 V leading to  $\mathbf{V}_{BAT,min} = 7.6 \text{ V}$ . If a very low minimum operating voltage is required,  $\mathbf{R}_{BAT}$  can be eliminated. In all other cases  $\mathbf{R}_{BAT}$  should be < 2 k $\Omega$ .

| Table 5. MOST IMPORTANT PARAMETERS TO |  |

|---------------------------------------|--|

| CALCULATE R <sub>BAT</sub>            |  |

| Symbol                                | Parameter                                                                         | AMIS-41682/3 |

|---------------------------------------|-----------------------------------------------------------------------------------|--------------|

| V <sub>BAT</sub>                      | Minimum operating<br>voltage at V <sub>BAT</sub> supply pin                       | 5 V          |

| I <sub>BAT</sub>                      | Max current in pin V <sub>BAT</sub><br>(5 V to 36 V) in all modes<br>of operation | 230 μΑ       |

| I <sub>BAT</sub> +<br>I <sub>CC</sub> | Max current in pin $V_{BAT}$ (5 V to 36 V) and $V_{CC}$ in low power mode         | 60 µA        |

| I <sub>RTL</sub>                      | Maximum RTL current in<br>low power modes                                         | 1.25 mA      |

## V<sub>CC</sub> Supply and Recommended Buffer Capacitance Introduction

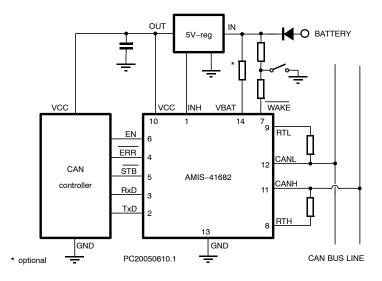

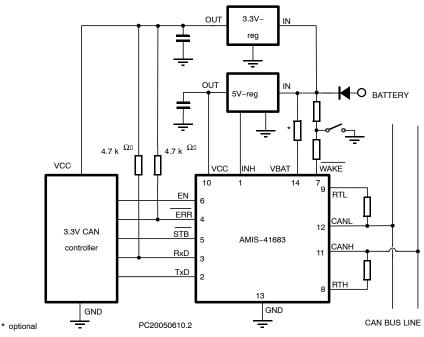

Two types of  $V_{CC}$  supply topologies can be recognized. For 5 V microcontrollers, in most cases, a common  $V_{CC}$  power supply is used for both the microcontroller and the AMIS-41682. (See Figure 1). In case of a 3.3 V microcontroller a separate  $V_{CC}$  supply is needed for the AMIS-41683 independently from the microcontroller. (See Figure 2).

Depending on the used topology the dimensioning of the buffer capacitor and the power dissipation in the voltage regulator will differ.

Figure 3. Single V<sub>CC</sub> Topology for 5 V Microcontroller

Figure 4. Dual V<sub>CC</sub> Topology for 3.3 V Microcontroller

#### Calculation

For calculating the power dissipation in the voltage regulator the average current consumption is important. For dimensioning the buffer capacitor the peak current and the peak duration time is of importance. gives an overview of the calculated values discussed further in this document. The average supply current is needed to calculate the thermal load of the required  $V_{CC}$  voltage regulator. The peak supply current may flow in case of certain bus failure conditions for a certain time and thus has an impact on the power supply buffering.

#### AND8366

The  $V_{CC}$  supply of the transceiver is recommended to support the characteristics as follows:

| Symbol                | Parameter                              | Condition          | AMIS-41682/3 |

|-----------------------|----------------------------------------|--------------------|--------------|

| I <sub>CC,av_NF</sub> | Average V <sub>CC</sub> supply current | No bus failure     | 31.15 mA     |

| I <sub>CC,av_SF</sub> | Average V <sub>CC</sub> supply current | Single bus failure | 66.15 mA     |

| I <sub>CC,pk_SF</sub> | Peak V <sub>CC</sub> supply current    | Single bus failure | 126 mA       |

| tSINGLE               | Over current duration                  | Single bus failure | < 6 Tbit     |

| I <sub>CC,pk_DF</sub> | Peak V <sub>CC</sub> supply current    | Dual bus failure   | 127 mA       |

| <b>t</b> DOUBLE       | Over current duration                  | Dual bus failure   | < 17 Tbit    |

In the following, these two cases are discussed in more detail.

## Calculating the Average Supply Current Without Bus Failure Condition

The average supply current is determined by the current consumption in the recessive state  $I_{cc\_rec}$  as listed in the datasheet and the current consumption in dominant state. The latter is the sum of the corresponding supply current  $I_{cc0\_dom}$ , the bus current  $I_{CANH\_dom}$  and the current in the termination resistor  $I_{CANH\_dom}$ .

The maximum dominant supply current (without bus wiring faults) is given by:

$$I_{CC\_dorm} = I_{CC0\_dom} + I_{CANH\_dom} + I_{RTL\_dom}$$

(eq. 5)

$$I_{\text{RTL}\_\text{dom}} = \frac{\left(V_{\text{CC}} - V_{\text{CANL}\_\text{dom}}\right)}{R_{\text{T}}} \qquad (\text{eq. 6})$$

Calculating with the given parameters in Table 7.

# Table 7. MOST IMPORTANT PARAMETERS TO CALCULATE THE MAXIMUM $\rm I_{OC}$ IN DOMINANT STATE

| Symbol                | Parameter                                             | AMIS-41682/3 |

|-----------------------|-------------------------------------------------------|--------------|

| I <sub>CC0_dom</sub>  | Max. V <sub>CC</sub> supply current dominant, no load | 12 mA        |

| I <sub>CANH_dom</sub> | Assumed CANH dominant<br>current                      | 40 mA        |

| R <sub>T</sub>        | Assumed termination res-<br>istor                     | 1 kΩ         |

| V <sub>CANL_dom</sub> | Assumed CANL dominant voltage                         | 1 V          |

Yields in:

$$I_{CC\_dom} = 12 \text{ mA} + 40 \text{ mA} + \frac{(5 \text{ V} - 1 \text{ V})}{1 \text{ k}\Omega} = 56 \text{ mA max}. \label{eq:ICC\_dom}$$

(Res.5)

The maximum recessive supply current (without bus wiring faults) is given by the parameters in Table 8:

#### Table 8. MAXIMUM ICC IN RECESSIVE STATE

| Symbol              | Parameter                                                       | AMIS-41682/3 |

|---------------------|-----------------------------------------------------------------|--------------|

| I <sub>CC_rec</sub> | Maximum V <sub>CC</sub> supply<br>current recessive, no<br>load | 6.3 mA       |

For thermal considerations the average supply current at pin  $V_{CC}$  is relevant considering the transmit duty cycle. The worst case condition is a continuously transmitting node. With an assumed transmit duty cycle of 50% on pin TxD, the maximum average supply current is:

$$I_{CC\_nom\_avg} = 0.5 * \left( I_{CC\_rec} + I_{CC\_dom} \right)$$

(eq. 7)

Using the parameter in and result (Res 5) in Equation 7 yields in:

$I_{CC\_nom\_avg} = 0.5 * (6.3 \text{ mA} + 56 \text{ mA}) = 31.15 \text{ mA max.}$ (Res.6)

#### Supply Currents With Single Bus Failure Condition

#### Average Supply Current in Single Fault Condition

The average supply current is determined by the current consumption in the recessive state  $I_{cc\_rec}$  as listed in the datasheet and the worst case current consumption in dominant state. The latter is the sum of the corresponding supply current  $I_{cc0\_dom}$ , the bus current when CANH is shorted to ground  $I_{CANH\_sc1\_dom}$  and the current in the termination resistor  $I_{CANH\_dom}$ .

The maximum dominant supply current (with SINGLE bus wiring faults CANH shorted to GND) is given by:

$$I_{CC\_sc1\_dom} = I_{CC0\_dom} + I_{CANH\_sc1\_dom} + I_{RTL\_dom}$$

(eq. 8)

Calculating with the given parameters in Table 9:

|        | Table 9. MAXIMUM DOMINANT CURRENT IN CASE<br>OF A SHORT CIRCUIT IN THE CANH PIN |              |

|--------|---------------------------------------------------------------------------------|--------------|

| Symbol | Parameter                                                                       | AMIS_41682/3 |

| Symbol                        | Parameter                            | AMIS-41682/3 |

|-------------------------------|--------------------------------------|--------------|

| I <sub>CANH_sc1_do</sub><br>m | CANH dominant current, short circuit | 110 mA       |

Yields in:

$$I_{CC\_sc1\_dom} = 12 \text{ mA} + 110 \text{ mA} + \frac{(5 \text{ V} - 1 \text{ V})}{1 \text{ k}\Omega} = 126 \text{ mA max.}$$

(Res.7)

For thermal considerations the average supply current at pin  $V_{CC}$  is relevant considering the transmit duty cycle. The worst case condition is a continuously transmitting node. With an assumed transmit duty cycle of 50% on pin TxD, the maximum average supply current is:

$$I_{CC\_sc1\_avg} = 0.5 * \left( I_{CC\_rec} + I_{CC\_sc1\_dom} \right)$$

(eq. 9)

Using the parameter from and and result (Res 7) in Equation 9 yields in:

#### Extra Supply Current in Single Fault Condition

Compared to the quiescent current in recessive state the maximum **extra** supply current when the CANH driver is turned on with CANH shorted to GND is needed to calculate the required worst case  $V_{CC}$  buffer capacitance. This extra supply current has to be buffered for up to 6-bit times. This 6-bit time limitation is set by the CAN controller which is supposed to send an error flag within this timing window.

$$\Delta I_{CC\_sc1} = I_{CC\_sc1\_dom} - I_{CC\_rec,min} \quad (eq. 10)$$

The minimum recessive supply current is given by the parameter in Table 10.

Table 10.  $V_{CC}$  MINIMUM CURRENT CONSUMPTION IN RECESSIVE STATE

| Symbol                  | Parameter                                                    | AMIS-41682/3 |

|-------------------------|--------------------------------------------------------------|--------------|

| I <sub>CC_rec,min</sub> | Min. V <sub>CC</sub> supply<br>current recessive, no<br>load | 1 mA         |

Using the parameter in and result (Res 7) in Equation 10 yields in:

$$\Delta I_{CC\_sc1} = 126 \text{ mA} - 1 \text{ mA} = 125 \text{ mA max.}$$

(Res.9)

## Worst–Case Max $V_{\mbox{CC}}$ Supply at Presence of a Dual Short Circuit

The worst case maximum  $V_{CC}$  supply current is flowing in case of a **dual short-circuit** of the bus. In this case the bus-lines CAN\_H and CAN\_L are shorted to ground and no communication is possible. Nevertheless the application supply should be able to deliver a proper  $V_{CC}$  for the microcontroller in order to prevent erroneous operation. For the calculation of the buffer capacitor we need to distinguish between the two supply topologies:

If there is a **separate** voltage regulator available supplying the transceiver exclusively (see Figure 5), **no care** has to be taken on this dual short circuit condition. If the voltage regulator enters the over-current protection level and its output will drop to limit the internal power dissipation, this under-voltage condition will only affect the function of the transceiver. The microcontroller is still powered properly by its own supply.

In case of a **shared** voltage supply for transceiver and microcontroller, this dual fault condition is relevant to dimension the required buffer capacitor.

## Max $V_{CC}$ Supply Current in Worst–Case Dual Fault Condition

$$I_{CC\_sc2\_dom} = I_{CC0\_dom} + I_{CANH\_sc1\_dom} + I_{RTL\_sc\_dom}$$

(t < 17 bit times) (eq. 11)

$$I_{\text{RTL}\_\text{sc}\_\text{dom}} = \frac{V_{\text{CC}}}{2} \qquad (\text{eq. 12})$$

The 17-bit time-out limitation is determined by the CAN protocol. Due to the dual fault condition with CANH and CANL shorted to GND the RxD pin of the transceiver is continuously clamped recessive (CANL to GND forces CANH operation; CANH is clamped recessive).

The moment the CAN controller starts a transmission, this dominant start of frame bit is not fed back via RxD and thus forces an error flag due to the bit failure condition (TX error counter increment by 8). This first bit of the error flag again is not reflected at RxD and forces the next error flag (TX error counter + 8).

Latest after 17 bit times, depending on the TX error counter level before starting this transmission, the CAN controller reaches the error passive limit (128) and stops sending dominant bits. Now a sequence of 25 recessive bits follows (8 bit error delimiter + 3 bit intermission + 8 bit suspend transmission) and the  $V_{CC}$  current becomes reduced to the recessive one. From now on only single dominant bits (start of frame) followed by 25 recessive bits (passive error flag + intermission + suspend transmission) are output until the CAN controller enters the bus off state.

So, for dimensioning the  $V_{CC}$  voltage source in this worst case dual failure scenario, up to 17 bit times might have to be buffered by a buffer capacitor depending on the regulation capabilities of the used voltage supply.

Using the parameters from and in Equations 11 and 12 yields in:

$$I_{CC\_sc2\_dom} = 12 \text{ mA} + 110 \text{ mA} + 5 \text{ V}/1 \text{ k}\Omega = 127 \text{ mA}$$

(Res.10)

#### V<sub>CC</sub> Extra Supply Current in Dual Fault Condition

Compared to the quiescent current in recessive state the maximum **extra** supply current when the CANH driver is

turned on in dual short–circuit condition is needed to calculate the required worst case  $V_{CC}$  buffer capacitance. This extra supply current has to be buffered for that time the applications voltage regulator needs to react.

$$\Delta I_{CC\_sc2} = I_{CC\_sc2\_dom} - I_{CC\_rec,min} \quad (eq. 13)$$

Using the parameter in and result (Res 10) in Equation (13) yields in:

$$\Delta I_{CC\_sc2} = 127 \text{ mA} - 1 \text{ mA} = 126 \text{ mA max.}$$

(Res.11)

#### Calculation of Worst-Case Buffer Capacitor

Depending on the power supply topology, the required worst-case buffer capacitor can be calculated.

In case of a **separate**  $V_{CC}$  supply for the transceiver only, the extra supply current  $\Delta I_{CC\_sc1}$  in case of the **single fault** condition has to be taken with a maximum of six dominant bit times.

$$C_{\text{BUFF}} = \Delta I_{\text{CC}\_\text{sc1}} * \frac{t_{\text{dom}\_\text{max}}}{\Delta V_{\text{max}}} \qquad (\text{eq. 14})$$

In case of a **shared**  $V_{CC}$  supply for transceiver and microcontroller, the extra supply current  $\Delta I_{CC\_sc2}$  in case of the **dual fault condition** has to be taken with a maximum of 17 dominant bit times.

$$C_{\text{BUFF}} = \Delta I_{\text{CC}\_\text{sc2}} * \frac{t_{\text{dom}\_\text{max}}}{\Delta V_{\text{max}}} \qquad (\text{eq. 15})$$

C<sub>BUFF</sub> at double fault

1000 1000 ΔV = 0,35 V  $\Delta V = 0,25 V$ C<sub>BUFF</sub> (uF) C<sub>BUFF</sub>(uF)  $\Delta V = 0,45 V$  $\Delta V = 0.35 V$ 100 100 = 0.45 V10 10 100 10 1000 10 100 1000 Speed (kBit/s) Speed (kBit/s)

Figure 5. Needed  $V_{CC}$  Buffer Capacitor for Single and Double Bus Failure

#### CBUFF Calculation for Shared Supply

In case of a shared supply concept the buffer capacitance has to be calculated based on the worst case dual fault condition in order to keep the micro–controller supply within the operating range:

Assuming a communication speed of 100 kBit/s gives:

$$t_{dom_max} = 17 * 10 \ \mu s = 170 \ \mu s$$

(Res.14)

Maximum allowed V<sub>CC</sub> voltage drop of 5% yields in:

- The buffer capacitor  $C_{BUFF}$  is calculated assuming the voltage regulator is **not** able to deliver any extra current within the maximum dominant output drive  $t_{dom_max}$  during the dual fault condition due to bandwidth limitations of the regulator.

- The voltage drop over the capacitor is assumed to be less than 5%. In the graphs also 7% and 9% are plotted.

#### C<sub>BUFF</sub> Calculation for <u>Separate</u> Supplied Transceiver

In case of a separate transceiver supply the buffer capacitance has to be calculated based on the single fault condition with CANH shorted to GND. Here the dual fault is not relevant.

Assuming a communication speed of 100kBit/s gives:

$$t_{dom max} = 6 * 10 \ \mu s = 60 \ \mu s$$

(Res.12)

Maximum allowed  $V_{CC}$  voltage drop of 5% yields in:

$$\Delta V_{max} = 0.25 V \qquad (Res.13)$$

Using the results (Res 9), (Res 12) and (Res 13) in Equation (14) yields in:

$$C_{BUFF} = 125 \text{ mA} * 60 \ \mu s / 0.25 \text{ V} = 30 \ \mu F$$

(eq. 16)

For different communication speeds and allowed voltage drop,  $C_{BUFF}$  can be looked up in the graph in Figure 5.

#### CBUFF at single fault

$\Delta V_{max} = 0.25 V$  (Res.15)

Using the results (Res 11), (Res 14) and (Res 15) in Equation 15 yields in:

$C_{BUFF} \,=\, 126 \; mA * 170 \& \mu s / 0.25 \; V \,=\, 85.7 \; \mu F \quad (Res.16)$

For different communication speeds and allowed voltage drop,  $C_{\rm BUFF}$  can be looked up in the graphs plotted in Figure 5.

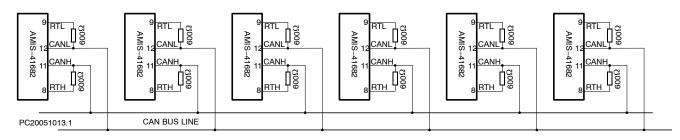

#### Calculation of Bus Termination Resistors and EMC Issues How to Dimension the Bus Termination Resistor Values – Some Basic Rules

The termination is provided by connecting the CANL line to the  $R_{TL}$  pins of the transceiver devices and by connecting the CANH line to the  $R_{TH}$  pins. By connecting the termination pins the following requirements have to be considered:

- The overall network termination resistor of one line (all parallel resistors connected to RTL or RTH pins) shall be about 100  $\Omega$ , due to in circuit current limitations and CAN voltage definitions.

- A single resistor connected to an individual transceiver device shall not be below 500 Ω, due to in circuit current limitations.

It is recommended, that every node provides its own termination resistors. However this is not a strict requirement. A not well terminated node might be sensitive for false wake up signals, if a broken line error had occurred.

Depending on the number of nodes in the network the local termination resistors can be calculated as:

$$R_{TI} = n * 100 \Omega$$

and  $R_{TH} = n * 100 \Omega$  (eq. 17)

Where n = number of nodes

If the number of nodes is smaller than five the network termination is limited to 500  $\Omega$ . This will lead to a non optimal line termination, but in small networks this is not considered as a problem.

#### Figure 6. Example Network with Six Nodes, 600 $\Omega$ Termination at Each Node

#### Tolerances of Bus Termination Resistors – EMC Considerations

The symmetry of the termination resistors within a single node has a major impact to the systems electromagnetic emission (EME) behavior. Thus it is important to have well matched termination resistors within each control unit. This means that the  $\mathbf{R}_{TH}$  resistor should have exactly the same value compared to the  $\mathbf{R}_{TL}$  resistor within one control unit in order to get the same time constant on each bus wire during signal transitions. The tolerance between two different control units is absolutely insignificant.

The principle to achieve a good EME performance is that the differential signal on the bus wires eliminates any emission due to compensation effects if both CAN wires are carrying exactly the same signal, but with inverse polarities.

Here the transceiver can only provide a perfect symmetry for the dominant transitions by design. The recessive transitions are mainly driven by the termination resistors and the network cables itself. So not only the transceiver's output drivers have an impact to the EME performance but also the termination and the cable symmetry.

It is obvious that also the layout of printed circuit boards has a significant impact to the EMC behavior if the CAN lines have different capacitive loads due to different wire lengths.

It is recommended to provide a termination resistor accuracy ( $\mathbf{R}_{TH}$  compared to  $\mathbf{R}_{TL}$ ) within the same node of 1% or lower. Also the bus cable has to be at least a twisted

pair cable in order to achieve a symmetrical capacitive load for both bus wires resulting in a good EMC performance.

#### Power Dissipation of Bus Termination Resistors R<sub>T</sub>

#### Average Power Dissipation – No Bus Failures

To determine the average power dissipation of the termination resistors, the average time between dominant and recessive bits has to be taken into account. Additionally a worst case ground shift is contributing to additional dissipation.

The power dissipation in recessive state is  $P_{rec} = 0$  because there is no voltage drop across the termination resistor.

In dominant state the dissipation is given by:

$$\mathsf{P}_{\mathsf{dom}} = \frac{\left(\mathsf{V}_{\mathsf{CC}} + \mathsf{V}_{\mathsf{GND}}\right)^2}{\mathsf{R}_{\mathsf{T}}} \qquad (\mathsf{eq. 18})$$

CAN frames are assumed to have a worst case ratio of dominant bits in the range of 0.75. This results in an average power dissipation calculated as follows:

$$P_{avg} = 0.25 P_{rec} + 0.75 P_{dom} = \frac{\left(0.75 * \left(V_{CC} + V_{GND}\right)\right)^2}{R_T}$$

(eq. 19)

Assuming  $R_T = 1 \text{ k}\Omega$  and a worst case ground shift of  $V_{GND}$ = 1.5 V yields in:

$$\mathsf{P}_{\mathsf{avg}} = \frac{\left(0.75 * (5 \text{ V} + 1.2 \text{ V})\right)^2}{1 \text{ k}\Omega} = 23.7 \text{ mW}$$

(Res.17)

#### **Maximum Peak Power Dissipation**

In case of a bus failure (CANH to  $V_{BAT}$ ) a peak current will flow in the termination resistor. However the duration is limited because after the maximum Failure Detection Time the termination resistor will be disabled from the circuit. The peak power can be calculated as:

$$\mathsf{P}_{\mathsf{peak}} = \frac{\mathsf{V}_{\mathsf{BAT},\mathsf{max}}^{2}}{\mathsf{R}_{\mathsf{T}}} \left( \mathsf{with \ duration} \ < \mathsf{t}_{\mathsf{det}} \right)$$

(eq. 20)

The maximum failure detection time is given by the parameter in Table 11:

#### Table 11. MAXIMUM FAILURE DETECTION TIME

| Symbol           | Parameter              | AMIS-41682/3 |

|------------------|------------------------|--------------|

| t <sub>det</sub> | Failure Detection time | 80 ms        |

Calculating with data from ,  $R_T$  = 1 k $\Omega$  and  $V_{BAT}$  = 27 V

$$P_{\text{peak}} = \frac{(27 \text{ V})^2}{1 \text{ k}\Omega} = 730 \text{ mW for less than 8 ms}$$

$$E_{\text{peak}} = 5.84 \text{ mJ}$$

(Res.18)

Because the energy  $\mathrm{E}_{\text{peak}}$  is very limited, this peak power dissipation can be neglected.

| Symbol                    | Description                                                                                                          |  |

|---------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| I <sub>cc_dom</sub>       | Supply current at pin $V_{CC}$ while driving a dominant bit with a certain load to the pins                          |  |

| I <sub>cc0_dom</sub>      | Supply current at pin $V_{CC}$ while driving a dominant bit <b>without</b> any load to the pins                      |  |

| I <sub>CANH_dom</sub>     | Output current of pin CANH while driving a dominant bit with nominal bus load of 100 $\Omega$ in total               |  |

| I <sub>RTL_dom</sub>      | Output current of pin RTL while driving a dominant bit with a certain load                                           |  |

| I <sub>cc_rec</sub>       | Supply current at pin $V_{CC}$ while driving a recessive bit                                                         |  |

| I <sub>cc_norm_avg</sub>  | Average supply current at pin $V_{CC}$ assuming no bus failure and continuous sending                                |  |

| I <sub>cc_sc1_dom</sub>   | Supply current at pin $V_{CC}$ driving a dominant bit while CANH is shorted to GND                                   |  |

| ICANH_sc1_dom             | Output current of pin CANH driving a dominant bit while CANH is shorted to GND                                       |  |

| I <sub>cc_sc1_avg</sub>   | Average supply current at pin V <sub>CC</sub> assuming CANH shorted to GND and continuous sending                    |  |

| $\Delta I_{cc\_sc1}$      | Supply current change at pin $V_{CC}$ in case a dominant bit is driven while CANH is shorted to GND                  |  |

| I <sub>cc_sc2_dom</sub>   | Supply current at pin $V_{CC}$ driving a dominant bit while CANH and CANL are shorted to GND                         |  |

| I <sub>RTL_sc_dom</sub>   | Output current of pin RTL while driving a dominant bit with CANL shorted to GND                                      |  |

| $\Delta I_{cc\_sc2}$      | Supply current change at pin V <sub>CC</sub> in case a dominant bit is driven while CANH and CANL are shorted to GND |  |

| V <sub>CC</sub>           | Supply voltage at pin $V_{CC}$                                                                                       |  |

| V <sub>CANL_dom</sub>     | Voltage level on CANL while a dominant bit is driven                                                                 |  |

| R <sub>T</sub>            | Termination resistor connected to pins RTL and RTH                                                                   |  |

| t <sub>dom_max</sub>      | Maximum possible continuous dominant drive time                                                                      |  |

| $\Delta \mathbf{V}_{max}$ | Maximum allowed voltage change at pin $V_{CC}$                                                                       |  |

| C <sub>BUFF</sub>         | Required buffer capacitance in case the voltage regulator does not deliver extra current within t <sub>dom_max</sub> |  |

| t <sub>PD(H)</sub>        | Typical propagation delay TxD to RxD (High)                                                                          |  |

| Ci                        | Input capacity seen from the open drain outputs                                                                      |  |

| R <sub>PU</sub>           | Pull up resistor 3.3 V open drain output                                                                             |  |

| V <sub>OL,max</sub>       | Maximum low level output voltage                                                                                     |  |

| I <sub>SINK</sub>         | Sink current in open drain output                                                                                    |  |

| R <sub>BAT</sub>          | Series resistor in V <sub>BAT</sub> connection                                                                       |  |

| V <sub>DROPN</sub>        | Voltage drop over V <sub>BAT</sub> series resistor in Normal mode                                                    |  |

| V <sub>DROPLP</sub>       | Voltage drop over V <sub>BAT</sub> series resistor in Low Power mode                                                 |  |

| V <sub>BAT</sub>          | Minimum operating voltage at V <sub>BAT</sub> supply pin                                                             |  |

| I <sub>BAT</sub>          | Max current in pin V <sub>BAT</sub> (5 to 36 V) in all modes of operation                                            |  |

### Table 12. GLOSSARY

#### Table 12. GLOSSARY

| Symbol                             | Description                                                                           |

|------------------------------------|---------------------------------------------------------------------------------------|

| I <sub>BAT</sub> + I <sub>CC</sub> | Max current in pin V <sub>BAT</sub> (5 to 36 V) and V <sub>CC</sub> in low power mode |

| I <sub>RTL</sub>                   | Maximum RTL current in low power modes                                                |

| I <sub>CC,av_NF</sub>              | Average V <sub>CC</sub> supply current                                                |

| I <sub>CC,av_SF</sub>              | Average V <sub>CC</sub> supply current                                                |

| I <sub>CC,pk_SF</sub>              | Peak V <sub>CC</sub> supply current                                                   |

| tSINGLE                            | Overcurrent duration                                                                  |

| I <sub>CC,pk_DF</sub>              | Peak V <sub>CC</sub> supply current                                                   |

| t <sub>DOUBLE</sub>                | Over current duration                                                                 |

| I <sub>CC,av_NF</sub>              | Average V <sub>CC</sub> supply current                                                |

| R <sub>TH</sub> ,R <sub>TL</sub>   | CAN bus termination resistors                                                         |

| t <sub>det</sub>                   | Failure detection time                                                                |

| P <sub>avg</sub>                   | Average power dissipation in CAN bus termination resistors                            |

| P <sub>peak</sub>                  | Peak power dissipation in CAN bus termination resistors                               |

| E <sub>peak</sub>                  | Peak energy in CAN bus termination resistors                                          |

ON Semiconductor and ()) are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application is intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized to subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5773–3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative